# S1D15719 Series Technical Manual

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2006, All rights reserved.

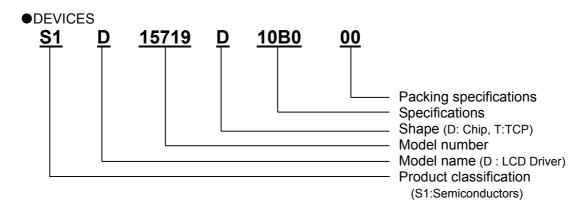

# Configuration of product number

# CONTENTS

| 3. BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1. | DES   | CRIPTION                                               | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|--------------------------------------------------------|----|

| 4. PIN ASSIGNMENT         4           4.1 Chip Assignment         4           4.2 Alignment mark         4           4.3 Pad Center Coordinates (COM interlace output type)         5           5. PIN DESCRIPTION         9           5.1 Power Pin         9           5.2 LCD Power Supply Current Pin         10           5.3 System Bus Connection Pin         11           5.4 Liquid Crystal drive pin         13           5.5 Thermal sensor pins         13           5.6 Pin for Test         13           6. FUNCTIONAL DESCRIPTION         14           6.1.1 Selection of Interface Type         14           6.1.2 parallel Interface         14           6.1.3 Serial Interface         14           6.1.4 Chip Selection of         15           6.1.5 Access to display data RAM and Internal register         15           6.1.5 Access to display data RAM and Internal register         15           6.2.2 Display data RAM         16           6.2.2 Display data RAM         16           6.2.2 Display data RAM         16           6.2.3 Oscillator circuit         17           6.3 Oscillator circuit         21           6.4 Display data latch circuit         18           6.3 Oscillator ci                                                                | 2. | FEA   | TURES                                                  | 2  |

| 4.1       Chip Assignment       4         4.2       Alignment mark       4         4.3       Pad Center Coordinates (COM interlace output type)       5         5       PIN DESCRIPTION       9         5.1       Power Pin       9         5.2       LCD Power Supply Current Pin.       10         5.3       System Bus Connection Pin       13         5.4       Liquid Crystal drive pin.       13         5.5       Thermal sensor pins       13         5.6       Pin for Test.       13         6.7       INPUNCTIONAL DESCRIPTION       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.1.5       Access to cisplay data RAM       16         6.2.2       Display data latch circuit       17         6.2.3       Page add                                                                                                                                                                     | 3. | BLO   | OCK DIAGRAM                                            | 3  |

| 4.2       Alignment mark.       4         4.3       Pad Center Coordinates (COM interlace output type)       5         5.       PIN DESCRIPTION       9         5.1       Power Pin       99         5.2       LCD Power Supply Current Pin       10         5.3       System Bus Connection Pin       11         5.4       Liquid Crystal drive pin       13         5.5       Thermal sensor pins       13         5.6       Pin for Test       13         5.6       FUNCTIONAL DESCRIPTION       14         6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.2       Display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.3       Page address circuit and column address circuit       17         6.2.3       Page address circuit       17         6.4                                                                                                                                                                            | 4. | PIN / | ASSIGNMENT                                             | 4  |

| 4.3       Pad Center Coordinates (COM interlace output type)       5         5.       PiN DESCRIPTION       9         5.1       Power Pin       9         5.2       LCD Power Supply Current Pin.       10         5.3       System Bus Connection Pin       11         5.4       Liquid Crystal drive pin.       13         5.5       Thermal sensor pins       13         5.6       Pin for Test.       13         6.7       FUNCTIONAL DESCRIPTION       14         6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.1.5       Access to display data RAM       16         6.2.2       Display data RAM       16         6.2.2       Display data RAM       16         6.2.3       Page address circuit and column address circuit       17         6.2.4       Line address circuit       18         6.2.5       Display timing generation circuit       21                                                                                                                                                     |    | 4.1   | Chip Assignment                                        | 4  |

| 5. PIN DESCRIPTION       9         5.1 Power Pin       9         5.2 LCD Power Supply Current Pin.       10         5.3 System Bus Connection Pin       11         5.4 Liquid Crystal drive pin       13         5.5 Thermal sensor pins       13         5.6 Pin for Test.       13         6. FUNCTIONAL DESCRIPTION.       14         6.1.1 Selection of Interface Type.       14         6.1.2 parallel Interface       14         6.1.3 Setial Interface       14         6.1.4 Chip Selection       15         6.1.5 Access to display data RAM       16         6.2.1 Display data RAM       16         6.2.2 Display of gray-scale       17         6.2.3 Page address circuit and column address circuit       17         6.2.4 Line address circuit       18         6.2.5 Display data latch circuit.       18         6.3 Oscillator circuit.       21         6.4 Lipe detection circuit       22         6.6.1 SEG Drivers       22         6.6.2 COM Drivers       22         6.6.3 Dummy Selection Period.       22         6.6.4 Sed Drivers       22         6.6.3 Dummy Selection Period.       22         6.7.4 Vsoyoltage regulating circuit       22<                                                                                                                    |    | 4.2   | Alignment mark                                         | 4  |

| 5.1       Power Pin       9         5.2       LCD Power Supply Current Pin.       10         5.3       System Bus Connection Pin       11         5.4       Liquid Crystal drive pin.       13         5.5       Thermal sensor pins       13         5.6       Pin for Test.       13         6.       FUNCTIONAL DESCRIPTION.       14         6.1.1       Selection of Interface Type.       14         6.1.2       parallel Interface       14         6.1.3       Selection of Interface Type.       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM       16         6.2.1       Display data RAM.       16         6.2.2       Display of gray-scale       17         6.2.3       Page address circuit and column address circuit       17         6.2.4       Line address circuit       18         6.2.5       Display data latch circuit.       21         6.4       Display data latch circuit.       22         6.6.1       SEG Drivers       22         6.6.2       COM Drivers       22         6.6.3       Dummy Selection Period.       22         6.7.1       <                                                                                                                                                                 |    | 4.3   | Pad Center Coordinates (COM interlace output type)     | 5  |

| 5.2       LCD Power Supply Current Pin.       10         5.3       System Bus Connection Pin       11         5.4       Liquid Crystal drive pin.       13         5.5       Thermal sensor pins       13         5.6       Pin for Test.       13         6.7       FUNCTIONAL DESCRIPTION.       14         6.1       MPU interface       14         6.1.2       parallel Interface Type.       14         6.1.2       parallel Interface       14         6.1.3       Secial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.1.5       Access to display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display of gray-scale       17         6.2.3       Page address circuit       17         6.2.4       Line address circuit       18         6.3       Oscillator circuit       21         6.4       Display data latch circuit       21         6.5       Operating mode detection circuit       22         6.6.1       SEG Drivers       22         6.6.2       COM                                                                                                                                                                     | 5. | PIN   | DESCRIPTION                                            | 9  |

| 5.3       System Bus Connection Pin       11         5.4       Liquid Crystal drive pin       13         5.5       Thermal sensor pins       13         5.6       Pin for Test       13         6.       FUNCTIONAL DESCRIPTION       14         6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.3       Page address circuit and column address circuit       17         6.2.4       Line address circuit       18         6.3       Oscillator circuit       21         6.4       Display timing generation circuit       21         6.4       Display timing generation circuit       22         6.6.1       SEG Drivers       22         6.6.2                                                                                                                                                                       |    | 5.1   | Power Pin                                              | 9  |

| 5.4       Liquid Crystal drive pin       13         5.5       Thermal sensor pins       13         5.6       Pin for Test       13         6.       FUNCTIONAL DESCRIPTION       14         6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.1.6       Display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.3       Page address circuit and column address circuit       17         6.2.3       Page address circuit and column address circuit       18         6.3       Oscillator circuit       18         6.3       Oscillator circuit       21         6.4       Display data latch circuit       22         6.6.1       SEG Drivers       22         6.6.2       COM Drivers       22         6.6.3       Dummy Selection Period       22         6.6.4                                                                                                                                                                        |    | 5.2   | LCD Power Supply Current Pin                           | 10 |

| 5.5       Thermal sensor pins       13         5.6       Pin for Test       13         6.       FUNCTIONAL DESCRIPTION       14         6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.1       Display of gray-scale       17         6.2.2       Display data RAM       16         6.2.2       Display data latch circuit       17         6.2.4       Line address circuit and column address circuit       17         6.2.4       Line address circuit       18         6.3       Oscillator circuit       21         6.4       Display data latch circuit       18         6.3       Oscillator circuit       21         6.4       Display timing generation circuit       22         6.6.1       SEG Drivers       22         6.6.2                                                                                                                                                                            |    | 5.3   | System Bus Connection Pin                              | 11 |

| 5.6       Pin for Test       13         6.       FUNCTIONAL DESCRIPTION       14         6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.2       Display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display of gray-scale       17         6.2.3       Page address circuit and column address circuit       17         6.2.4       Line address circuit and column address circuit       18         6.3       Oscillator circuit       21         6.4       Display data latch circuit       21         6.5       Operating mode detection circuit       21         6.6       Liquid crystal drive circuit       22         6.6.1       SEG Drivers       22         6.6.2       COM Drivers       22         6.6.3       Dummy Selection Period       22         6.7       Power Supply Circuit       22                                                                                                                                                                |    | 5.4   | Liquid Crystal drive pin                               | 13 |

| 6. FUNCTIONAL DESCRIPTION       14         6.1 MPU interface       14         6.1.1 Selection of Interface Type       14         6.1.2 parallel Interface       14         6.1.3 Serial Interface       14         6.1.4 Chip Selection       15         6.1.5 Access to display data RAM and Internal register       15         6.2 Display data RAM       16         6.2.1 Display data RAM       16         6.2.2 Display of gray-scale       17         6.2.3 Page address circuit and column address circuit       17         6.2.4 Line address circuit       18         6.3 Oscillator circuit.       21         6.4 Display tata latch circuit.       18         6.5 Operating mode detection circuit       21         6.6 Liquid crystal drive circuit.       22         6.6.1 SEG Drivers       22         6.6.2 COM Drivers       22         6.6.3 Dummy Selection Period.       22         6.7 Power Supply Circuit.       22         6.7.1 Blocks of power supply circuit and combinations of their operations.       23         6.7.2 1st booster circuit.       29         6.7.4 V3 voltage regulating circuit.       29         6.7.5 Liquid crystal drive voltage generation circuit.       32 <td< td=""><td></td><td>5.5</td><td>Thermal sensor pins</td><td> 13</td></td<> |    | 5.5   | Thermal sensor pins                                    | 13 |

| 6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.2       Display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.3       Page address circuit and column address circuit       17         6.2.3       Page address circuit       18         6.2.4       Line address circuit       18         6.2.5       Display data latch circuit       18         6.3       Oscillator circuit       21         6.4       Display timing generation circuit       21         6.5       Operating mode detection circuit       22         6.6.1       SEG Drivers       22         6.6.2       COM Drivers       22         6.6.3       Dummy Selection Period       22         6.7       Power Supply Circuit       22         6.7.1       Blocks of power supply circuit and combinations of their operations <td< td=""><td></td><td>5.6</td><td>Pin for Test</td><td> 13</td></td<>                                                                |    | 5.6   | Pin for Test                                           | 13 |

| 6.1       MPU interface       14         6.1.1       Selection of Interface Type       14         6.1.2       parallel Interface       14         6.1.3       Serial Interface       14         6.1.4       Chip Selection       15         6.1.5       Access to display data RAM and Internal register       15         6.2       Display data RAM       16         6.2.1       Display data RAM       16         6.2.2       Display data RAM       16         6.2.3       Page address circuit and column address circuit       17         6.2.3       Page address circuit       18         6.2.4       Line address circuit       18         6.2.5       Display data latch circuit       18         6.3       Oscillator circuit       21         6.4       Display timing generation circuit       21         6.5       Operating mode detection circuit       22         6.6.1       SEG Drivers       22         6.6.2       COM Drivers       22         6.6.3       Dummy Selection Period       22         6.7       Power Supply Circuit       22         6.7.1       Blocks of power supply circuit and combinations of their operations <td< td=""><td>6.</td><td>FUN</td><td>CTIONAL DESCRIPTION</td><td> 14</td></td<>                                                       | 6. | FUN   | CTIONAL DESCRIPTION                                    | 14 |

| 6.1.2parallel Interface146.1.3Serial Interface146.1.4Chip Selection156.1.5Access to display data RAM and Internal register156.2Display data RAM166.2.1Display data RAM166.2.2Display of gray-scale176.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit216.4Display data latch circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |                                                        |    |

| 6.1.2parallel Interface146.1.3Serial Interface146.1.4Chip Selection156.1.5Access to display data RAM and Internal register156.2Display data RAM166.2.1Display data RAM166.2.2Display of gray-scale176.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit216.4Display data latch circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 6.1.1 Selection of Interface Type                      | 14 |

| 6.1.4Chip Selection156.1.5Access to display data RAM and Internal register156.2Display data RAM166.2.1Display data RAM166.2.2Display of gray-scale176.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit216.4Display data latch circuit216.5Operating mode detection circuit216.6SEG Drivers226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |                                                        |    |

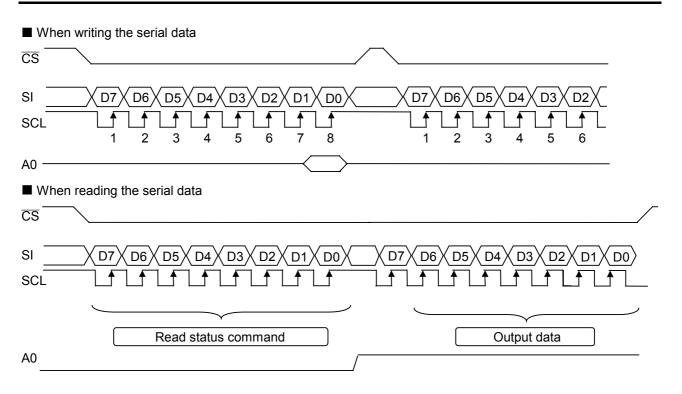

| 6.1.5Access to display data RAM and Internal register156.2Display data RAM166.2.1Display data RAM166.2.2Display of gray-scale176.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit186.3Oscillator circuit216.4Display timing generation circuit216.5Operating mode detection circuit216.6SEG Drivers226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |       | 6.1.3 Serial Interface                                 | 14 |

| 6.2Display data RAM166.2.1Display data RAM166.2.2Display of gray-scale176.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.2.6Display data latch circuit186.3Oscillator circuit216.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit216.6SEG Drivers226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       | 6.1.4 Chip Selection                                   | 15 |

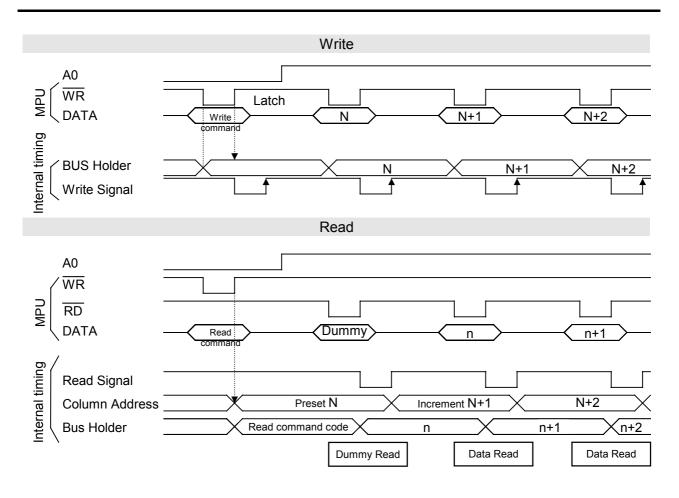

| 6.2.1Display data RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |       | 6.1.5 Access to display data RAM and Internal register | 15 |

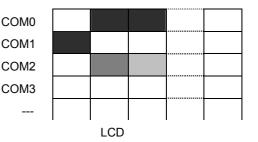

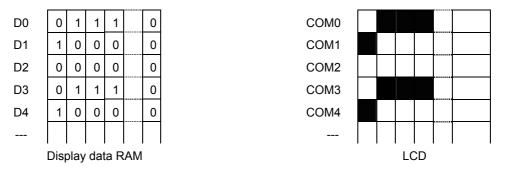

| 6.2.2Display of gray-scale176.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit186.3Oscillator circuit216.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 6.2   | Display data RAM                                       | 16 |

| 6.2.3Page address circuit and column address circuit176.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit216.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit296.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |       | 6.2.1 Display data RAM                                 | 16 |

| 6.2.4Line address circuit186.2.5Display data latch circuit186.3Oscillator circuit216.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       |                                                        |    |

| 6.2.5Display data latch circuit.186.3Oscillator circuit.216.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit.216.6SEG Drivers226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit.226.7.1Blocks of power supply circuit and combinations of their operations.236.7.21st booster circuit296.7.4V3 voltage regulating circuit.296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit.33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                                        |    |

| 6.3Oscillator circuit.216.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       |                                                        |    |

| 6.4Display timing generation circuit216.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       |                                                        |    |

| 6.5Operating mode detection circuit216.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       |                                                        |    |

| 6.6Liquid crystal drive circuit226.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | -     |                                                        |    |

| 6.6.1SEG Drivers226.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit.226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                                        |    |

| 6.6.2COM Drivers226.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 6.6   | · •                                                    |    |

| 6.6.3Dummy Selection Period226.7Power Supply Circuit226.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       |                                                        |    |

| 6.7Power Supply Circuit.226.7.1Blocks of power supply circuit and combinations of their operations.236.7.21st booster circuit276.7.32nd booster circuit.296.7.4V3 voltage regulating circuit.296.7.5Liquid crystal drive voltage generation circuit.326.7.6Temperature gradient selection circuit.326.8Examples of peripheral circuits of power supply circuit.33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                                        |    |

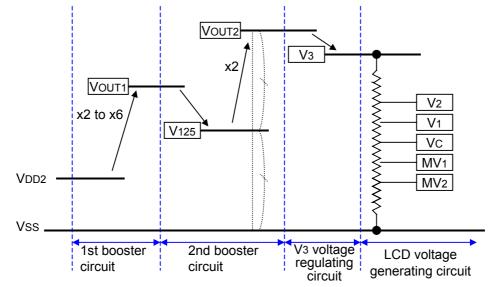

| 6.7.1Blocks of power supply circuit and combinations of their operations236.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.7.6Temperature gradient selection circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 07    | -                                                      |    |

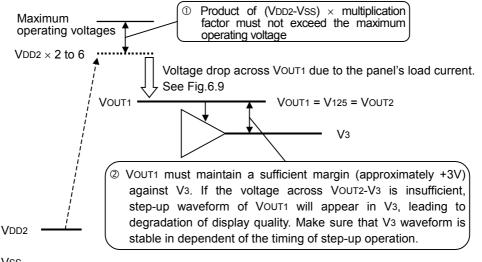

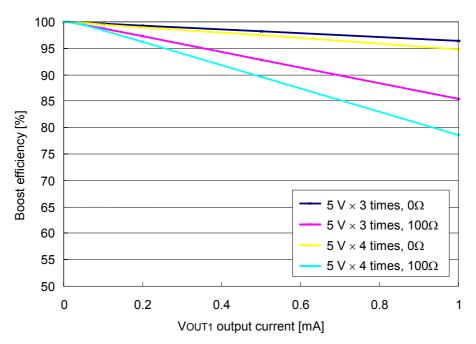

| 6.7.21st booster circuit276.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.7.6Temperature gradient selection circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 0.7   |                                                        |    |

| 6.7.32nd booster circuit296.7.4V3 voltage regulating circuit296.7.5Liquid crystal drive voltage generation circuit326.7.6Temperature gradient selection circuit326.8Examples of peripheral circuits of power supply circuit33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       |                                                        |    |

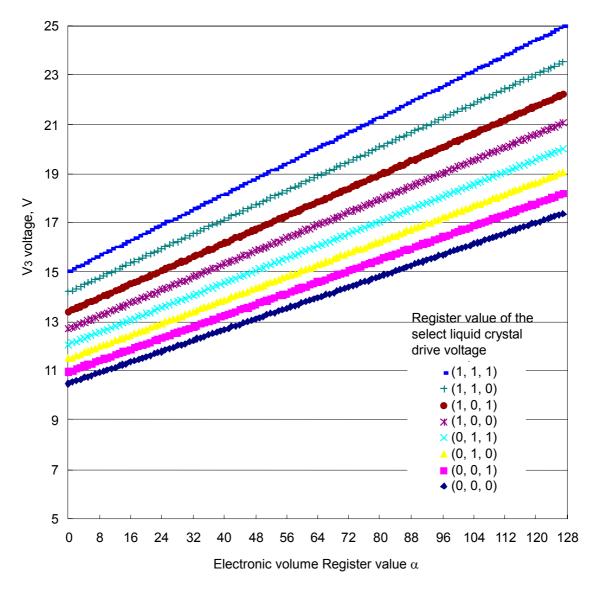

| <ul> <li>6.7.4 V3 voltage regulating circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |                                                        |    |

| <ul> <li>6.7.5 Liquid crystal drive voltage generation circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |                                                        |    |

| 6.7.6Temperature gradient selection circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |                                                        |    |

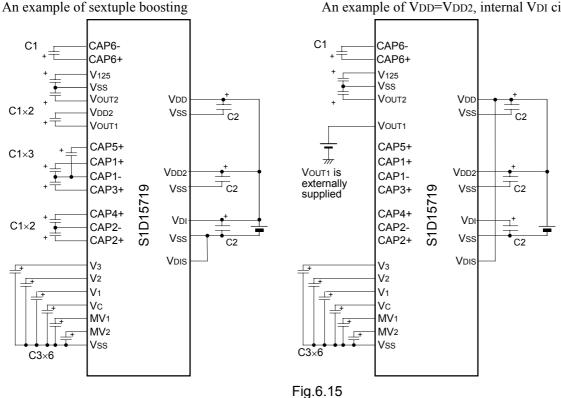

| 6.8 Examples of peripheral circuits of power supply circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |                                                        |    |

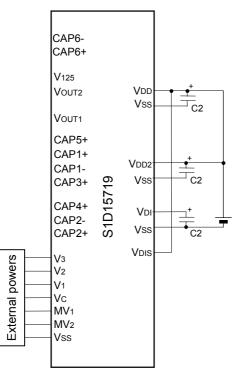

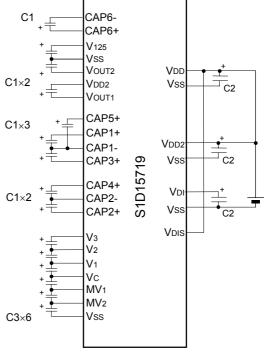

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 6.8   |                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 0.0   |                                                        |    |

|     |      | 6.8.2     | When using the 2nd booster circuit, V3 voltage regulating circuit and               |    |

|-----|------|-----------|-------------------------------------------------------------------------------------|----|

|     |      |           | LCD-voltage generating circuit (2nd booster circuit is turned off)                  | 33 |

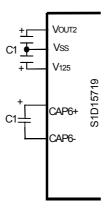

|     |      | 6.8.3     | When using the 1st booster circuit, V3 voltage regulating circuit and               |    |

|     |      |           | LCD-voltage generating circuit (2nd booster circuit is turned off)                  |    |

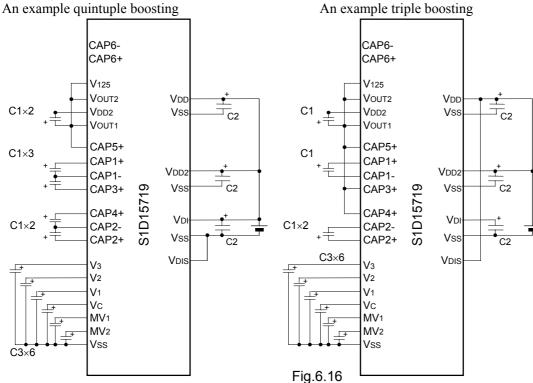

|     |      | 6.8.4     | When using V3 voltage regulating circuit and LCD-voltage generating current $\dots$ |    |

|     |      | 6.8.5     | When using LCD voltage generating circuit                                           |    |

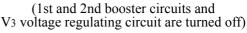

|     |      | 6.8.6     | All internal power supplies are turned off                                          |    |

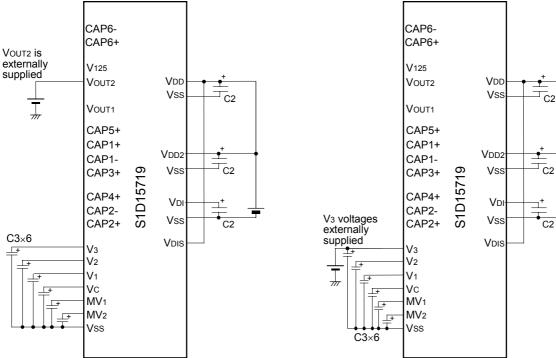

|     |      | 6.8.7     | Another example of connecting capacitor for LCD voltage                             |    |

|     |      | 6.8.8     | Reference values for capacitor setup                                                |    |

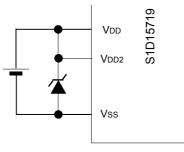

|     |      | 6.8.9     | Precautions of VDD2 power supply circuits                                           |    |

|     |      |           | ions on using COG                                                                   |    |

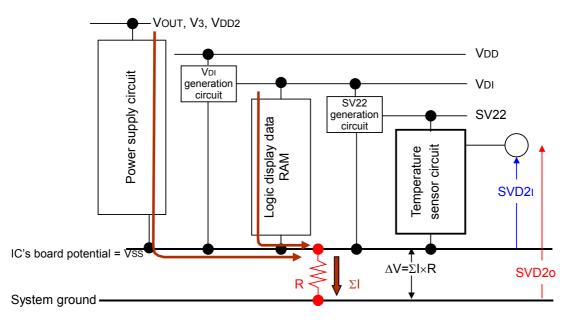

|     | 6.10 |           | I sensor circuit                                                                    |    |

|     |      |           | Analog voltage output element                                                       |    |

|     | ~    |           | Precautions                                                                         |    |

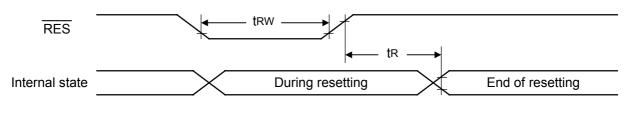

|     | 6.11 | Reset c   | ircuit                                                                              | 38 |

| 7.  | COM  |           |                                                                                     |    |

|     | 7.1  | Comma     | nd Description                                                                      | 39 |

|     | 7.2  |           | Commands                                                                            |    |

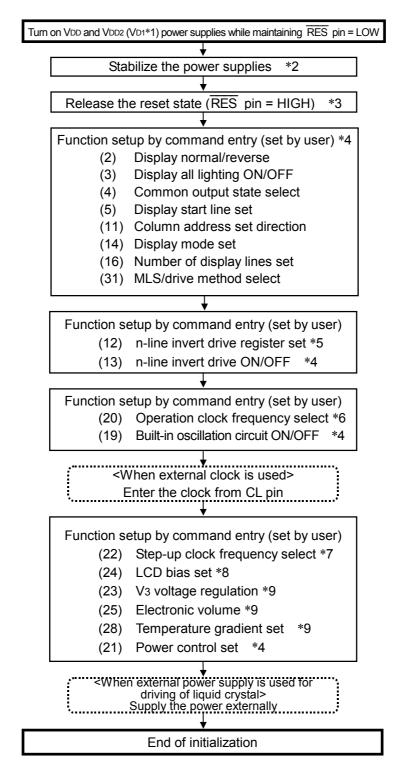

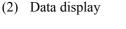

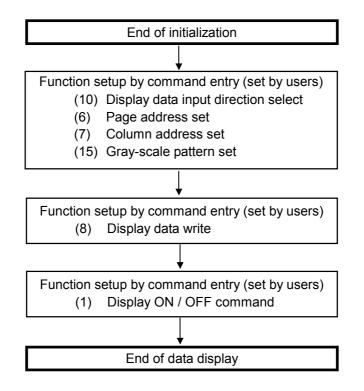

|     | 7.3  | Instructi | on Setup Example (Reference)                                                        | 59 |

| 8.  | ABS  | OLUTE     | MAXIMUM RATINGS                                                                     | 64 |

| 9.  | DC C | HARAC     | TERISTICS                                                                           | 65 |

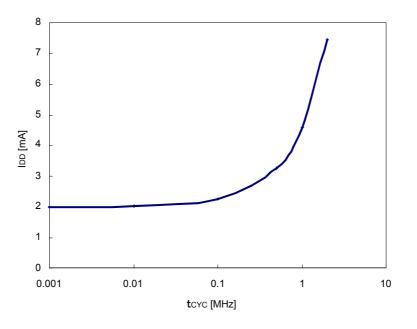

|     | 9.1  | Dynami    | c current consumption value                                                         | 66 |

|     |      | 9.1.1     | When the built-in power supplied is turned OFF                                      |    |

|     |      | 9.1.2     | When the built-in power supply is turned ON                                         | 67 |

|     | 9.2  | Current   | Consumption under Power Saving Mode                                                 | 68 |

|     | 9.3  | Referen   | ce Data                                                                             | 69 |

|     |      | 9.3.1     | While access from MPU is taking place                                               | 69 |

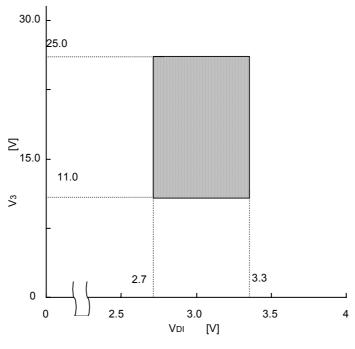

|     |      | 9.3.2     | Operating voltage rang of VDI system and V3 system                                  | 69 |

|     |      | 9.3.3     | Liquid crystal frame frequency free                                                 |    |

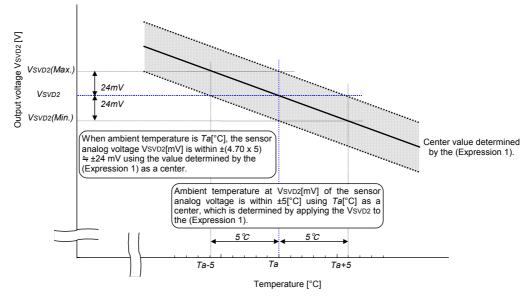

|     | 9.4  | Charact   | eristics of Thermal Sensor                                                          |    |

|     |      | 9.4.1     | Analog voltage output characteristics                                               | 70 |

| 10. | тімі | NG CHA    | RACTERICTICS                                                                        | 72 |

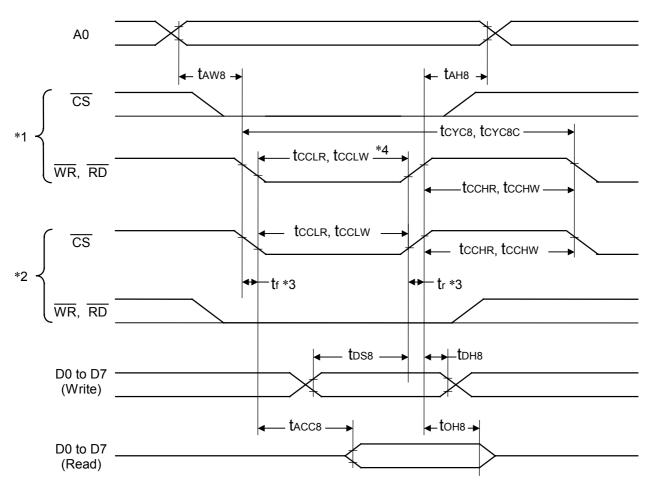

|     | 10.1 | System    | path read/write characteristics 1 (80 system MPU)                                   | 72 |

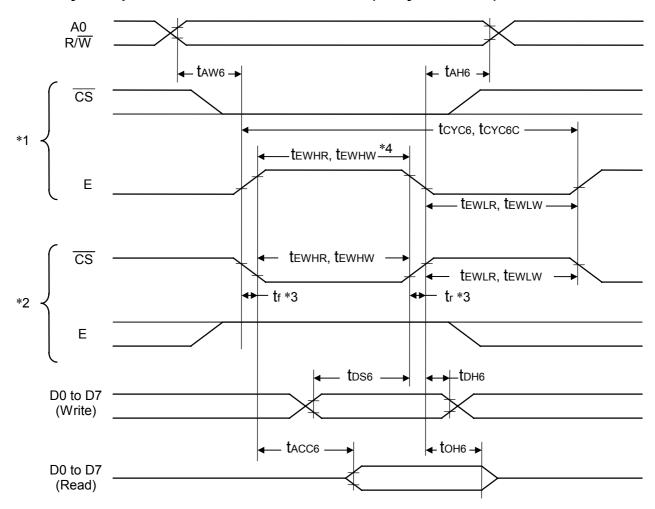

|     | 10.2 | System    | path read/write characteristics 2 (68 system MPU)                                   | 74 |

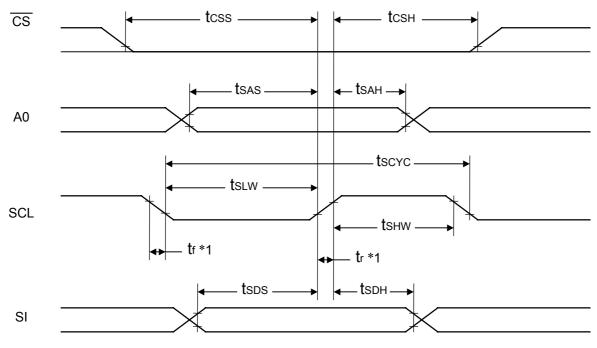

|     |      |           | iterface                                                                            |    |

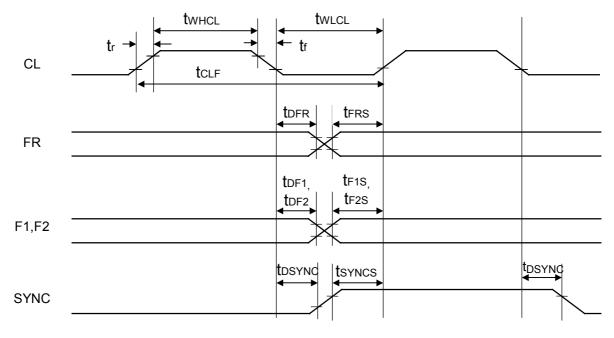

|     | 10.4 | Display   | Control Input and Output Timing                                                     | 77 |

|     |      |           | nput timing                                                                         |    |

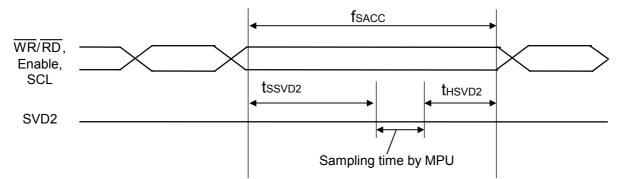

|     | 10.6 | Tempera   | ature Sensor Measuring Timing                                                       | 78 |

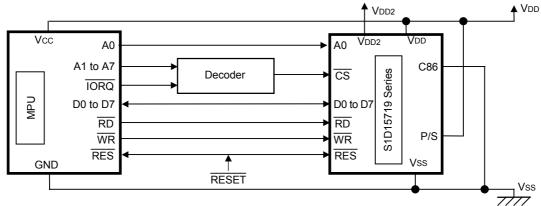

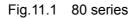

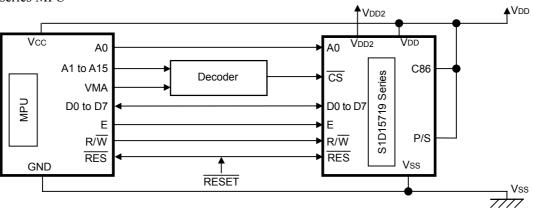

| 11. | MPU  | INTERF    | ACE (Reference Example)                                                             | 79 |

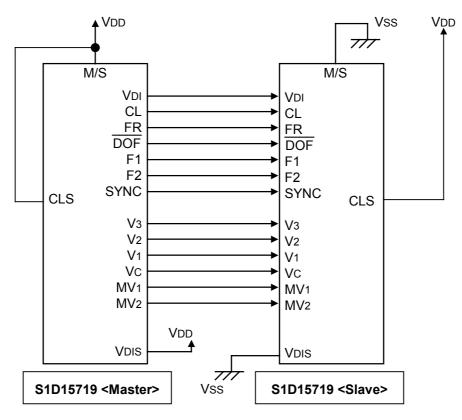

| 12. | CON  | NECTIO    | N BETWEEN LCD DRIVERS (Reference Example)                                           | 80 |

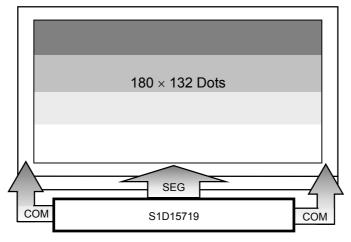

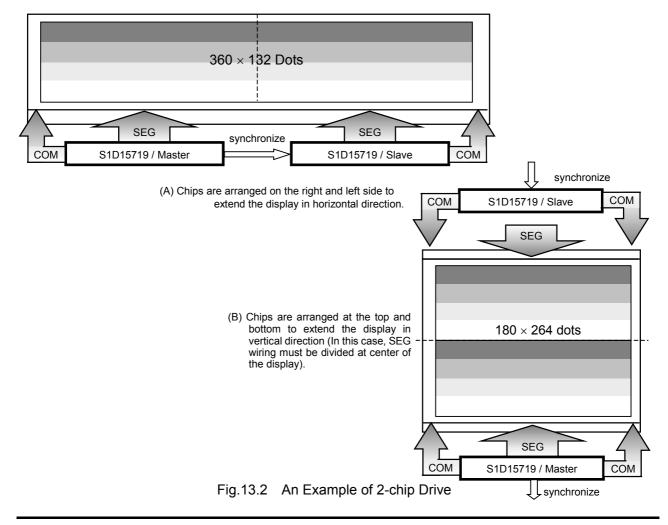

| 13. | LCD  | PANEL     | WIRING (Reference Example)                                                          | 81 |

| 14. | CAU  | TIONS     |                                                                                     | 82 |

# 1. **DESCRIPTION**

S1D15719 Series is a single chip MLS driver for dot matrix liquid crystal displays which can be directly connected to the microcomputer bus. It accepts the 8-bit parallel or serial display data from the microcomputer to store the data in the on-chip display data RAM, and issues liquid crystal drive signals independently of the microcomputer.

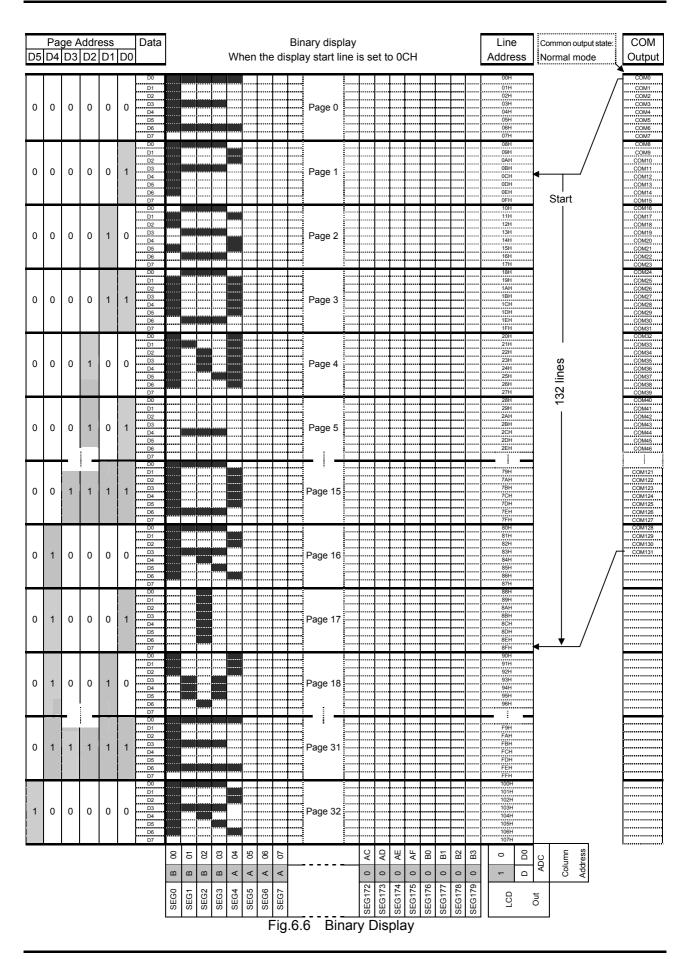

The S1D15719 Series provides both 4 gray-scale display and binary display. It incorporates a display data RAM ( $180 \times 132 \times 2$  bits). In the case of 4 gray-scale display, 2 bits of the on-chip RAM respond to one-dot pixels, while in the case of binary display, 1 bit of the on-chip RAM respond to one-dot pixels.

The S1D15719 Series features 132 common output circuits and 180 segment output circuits. A single chip provides a display of 11 characters by 8 lines with  $180 \times 132$  dots ( $16 \times 16$  dots) and display of 15 characters by 11 lines by the  $12 \times 12$  dot character font.

S1D15719 Series can be used to constitute a system to provide optimum LCD contrast throughout a wide temperature range without need for use of supplementary parts such as the thermistor, under controls of a microcomputer.

# 2. FEATURES

- Direct RAM data display by display data RAM

- 4 gray-scale display (Normally white in normal display mode)

- RAM bit data (MSB, LSB)

- (1,1): gray-scale 3, black

- (1,0): gray-scale 2

- (0,1): gray-scale 1

- (0,0): gray-scale 0, white

- Binary display (Normally white display is in normal mode)

- RAM bit data

- "1": On and black

- "0": Off and white

- RAM capacity

- $132 \times 180 \times 2 = 47,520$  bits

- Liquid crystal drive circuit

- 132 common outputs and 180 segment outputs

- High-speed 8-bit MPU interface (directly connectable to the MPUs of both 80/68 series) / serial interface possible

- A variety of command functions Duty set, n-line reversal, display data RAM address control, contrast control, display ON/OFF, display normal/reverse rotation, display all lighting ON/OFF, liquid crystal drive power supply circuit control, display clock built-in oscillator circuit control

- MLS drive technology Built-in high precision voltage regulation function

- High precision CR oscillator circuit incorporated

- Low power consumption

- Built-in temperature sensor circuit

- Power supply

- Logic power supply 1: VDI-VSS= 2.7V to 3.3V Logic power supply 2: VDD-VSS= 2.7V to 5.5V Booster power supply: VDD2-VSS= VDD to 5.5V Liquid crystal drive power supply: V3-VSS= 11V to 25V

- Wide operation temperature range: -40 to +85°C

- CMOS process

- Shipping form: Bare chips

- Light and radiation proof measures are not taken in designing.

Series Specification

| Product name    | Shipping style | Chip thickness | Specification        |

|-----------------|----------------|----------------|----------------------|

| S1D15719D10B000 | Bare chip      | 0.625mm        | COM interlace output |

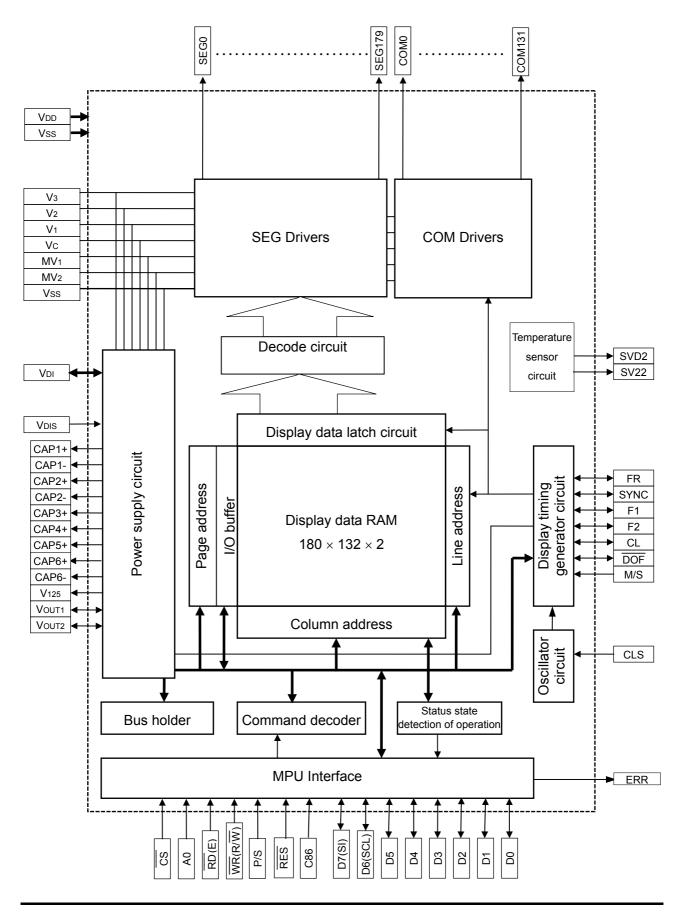

# 3. BLOCK DIAGRAM

# 4. PIN ASSIGNMENT

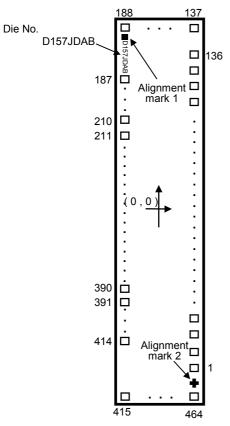

# 4.1 Chip Assignment

| lt        | em         | х    | Size   | Y     | Unit |

|-----------|------------|------|--------|-------|------|

| Chi       | o size     | 3.03 | ×      | 17.27 | mm   |

| Chip th   | nickness   |      | 0.625  |       | mm   |

| Bum       | p pitch    |      | Min.50 |       | μm   |

| Bump size |            |      |        |       |      |

| PAD No.   | 1 to 136   | 85   | ×      | 85    | μm   |

|           | 137 to 186 | 33   | ×      | 106   | μm   |

|           | 187 to 210 | 106  | ×      | 33    | μm   |

|           | 211 to 390 | 106  | ×      | 52    | μm   |

|           | 391 to 414 | 106  | ×      | 33    | μm   |

|           | 415 to 464 | 33   | ×      | 106   | μm   |

| Bump      | height     |      | Тур.17 |       | μm   |

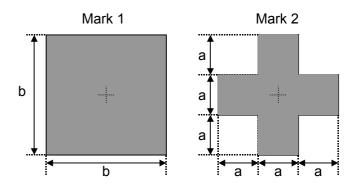

# 4.2 Alignment mark

Alignment coordinate

| 1 | (-1365, 8055) µm |

|---|------------------|

| 2 | (1365, -8252) µm |

Mark size

$a = 15 \ \mu m$  $b = 45 \ \mu m$

# 4.3 Pad Center Coordinates (COM interlace output type)

Unit: µm

| PAD | Pin                                 |      | 1     | PAD | Pin   |      |       | PAD | Pin    |      | Jnit: μm |

|-----|-------------------------------------|------|-------|-----|-------|------|-------|-----|--------|------|----------|

| No. | Name                                | X    | Y     | No. | Name  | X    | Y     | No. | Name   | X    | Y        |

| 1   | NC                                  | 1361 | -8100 | 51  | Vdd   | 1361 | -2100 | 101 | CAP6+  | 1361 | 3900     |

| 2   | NC                                  |      | -7980 | 52  | Vdd   |      | -1980 | 102 | CAP6-  |      | 4020     |

| 3   | Vdd                                 |      | -7860 | 53  | Vdd   |      | -1860 | 103 | CAP6-  |      | 4140     |

| 4   | Vdis                                |      | -7740 | 54  | Vdd2  |      | -1740 | 104 | CAP6-  |      | 4260     |

| 5   | Vss                                 |      | -7620 | 55  | Vdd2  |      | -1620 | 105 | CAP6-  |      | 4380     |

| 6   | SYNC                                |      | -7500 | 56  | Vdd2  |      | -1500 | 106 | V3     |      | 4500     |

| 7   | FR                                  |      | -7380 | 57  | Vdd2  |      | -1380 | 107 | V3     |      | 4620     |

| 8   | CL                                  |      | -7260 | 58  | VOUT1 |      | -1260 | 108 | V3     |      | 4740     |

| 9   | DOF                                 |      | -7140 | 59  | VOUT1 |      | -1140 | 109 | V2     |      | 4860     |

| 10  | F1                                  |      | -7020 | 60  | VOUT1 |      | -1020 | 110 | V2     |      | 4980     |

| 11  | F2                                  |      | -6900 | 61  | VOUT1 |      | -900  | 111 | V2     |      | 5100     |

| 12  | Vss                                 |      | -6780 | 62  | CAP1+ |      | -780  | 112 | V1     |      | 5220     |

| 13  | ERR                                 |      | -6660 | 63  | CAP1+ |      | -660  | 113 | V1     |      | 5340     |

| 14  | NC                                  |      | -6540 | 64  | CAP1+ |      | -540  | 114 | V1     |      | 5460     |

| 15  | CS                                  |      | -6420 | 65  | CAP1+ |      | -420  | 115 | Vc     |      | 5580     |

| 16  | RES                                 |      | -6300 | 66  | CAP1- |      | -300  | 116 | Vc     |      | 5700     |

| 17  | A0                                  |      | -6180 | 67  | CAP1- |      | -180  | 117 | Vc     |      | 5820     |

| 18  | Vss                                 |      | -6060 | 68  | CAP1- |      | -60   | 118 | MV1    |      | 5940     |

| 19  | $\overline{WR}$ , R/ $\overline{W}$ |      | -5940 | 69  | CAP1- |      | 60    | 119 | MV1    |      | 6060     |

| 20  | RD, E                               |      | -5820 | 70  | CAP3+ |      | 180   | 120 | MV1    |      | 6180     |

| 21  | Vdd                                 |      | -5700 | 71  | CAP3+ |      | 300   | 121 | MV2    |      | 6300     |

| 22  | D7, SI                              |      | -5580 | 72  | CAP3+ |      | 420   | 122 | MV2    |      | 6420     |

| 23  | D6, SCL                             |      | -5460 | 73  | CAP3+ |      | 540   | 123 | MV2    |      | 6540     |

| 24  | D0                                  |      | -5340 | 74  | CAP5+ |      | 660   | 124 | Vss    |      | 6660     |

| 25  | D1                                  |      | -5220 | 75  | CAP5+ |      | 780   | 125 | Vss    |      | 6780     |

| 26  | D2                                  |      | -5100 | 76  | CAP5+ |      | 900   | 126 | TESTA  |      | 6900     |

| 27  | D3                                  |      | -4980 | 77  | CAP5+ |      | 1020  | 127 | TESTB  |      | 7020     |

| 28  | D4                                  |      | -4860 | 78  | VOUT1 |      | 1140  | 128 | TESTB  |      | 7140     |

| 29  | D5                                  |      | -4740 | 79  | CAP4+ |      | 1260  | 129 | TEST3  |      | 7260     |

| 30  | D6, SCL                             |      | -4620 | 80  | CAP4+ |      | 1380  | 130 | TEST4  |      | 7380     |

| 31  | D7, SI                              |      | -4500 | 81  | CAP4+ |      | 1500  | 131 | Vdi    |      | 7500     |

| 32  | Vdd                                 |      | -4380 | 82  | CAP4+ |      | 1620  | 132 | SVD2   |      | 7620     |

| 33  | M/S                                 |      | -4260 | 83  | CAP2- |      | 1740  | 133 | SV22   |      | 7740     |

| 34  | CLS                                 |      | -4140 | 84  | CAP2- |      | 1860  | 134 | TEST5  |      | 7860     |

| 35  | Vss                                 |      | -4020 | 85  | CAP2- |      | 1980  | 135 | NC     |      | 7980     |

| 36  | TEST1                               |      | -3900 | 86  | CAP2- |      | 2100  | 136 | NC     | •    | 8100     |

| 37  | C86                                 |      | -3780 | 87  | CAP2+ |      | 2220  | 137 | NC     | 1224 | 8469     |

| 38  | P/S                                 |      | -3660 | 88  | CAP2+ |      | 2340  | 138 | COM129 | 1174 |          |

| 39  | Vdd                                 |      | -3540 | 89  | CAP2+ |      | 2460  | 139 | COM128 | 1124 |          |

| 40  | Vss                                 |      | -3420 | 90  | CAP2+ |      | 2580  | 140 | COM123 | 1074 |          |

| 41  | Vss                                 |      | -3300 | 91  | VOUT1 |      | 2700  | 141 | COM122 | 1024 |          |

| 42  | Vss                                 |      | -3180 | 92  | Vout2 |      | 2820  | 142 | COM121 | 974  |          |

| 43  | Vss                                 |      | -3060 | 93  | VOUT2 |      | 2940  | 143 | COM120 | 924  |          |

| 44  | Vss                                 |      | -2940 | 94  | VOUT2 |      | 3060  | 144 | COM115 | 874  |          |

| 45  | Vss                                 |      | -2820 | 95  | Vout2 |      | 3180  | 145 | COM114 | 824  |          |

| 46  | TEST2                               |      | -2700 | 96  | V125  |      | 3300  | 146 | COM113 | 774  |          |

| 47  | Vdi                                 |      | -2580 | 97  | V125  |      | 3420  | 147 | COM112 | 724  |          |

| 48  | Vdi                                 |      | -2460 | 98  | CAP6+ |      | 3540  | 148 | COM107 | 674  |          |

| 49  | Vdi                                 |      | -2340 | 99  | CAP6+ |      | 3660  | 149 | COM106 | 624  |          |

| 50  | Vdd                                 | . ↓  | -2220 | 100 | CAP6+ |      | 3780  | 150 | COM105 | 574  | <b>↓</b> |

Unit: µm

| PAD | Pin    |       |      | PAD | Pin   |       |      | PAD | Pin   |       | Jnn. μm |

|-----|--------|-------|------|-----|-------|-------|------|-----|-------|-------|---------|

| No. | Name   | Х     | Y    | No. | Name  | х     | Y    | No. | Name  | X     | Y       |

| 151 | COM104 | 524   | 8469 | 201 | COM9  | -1350 | 7257 | 251 | SEG40 | -1350 | 3713    |

| 152 | COM99  | 475   |      | 202 | COM8  |       | 7207 | 252 | SEG41 |       | 3638    |

| 153 | COM98  | 425   |      | 203 | COM3  |       | 7157 | 253 | SEG42 |       | 3563    |

| 154 | COM97  | 375   |      | 204 | COM2  |       | 7107 | 254 | SEG43 |       | 3488    |

| 155 | COM96  | 325   |      | 205 | COM1  |       | 7057 | 255 | SEG44 |       | 3413    |

| 156 | COM91  | 275   |      | 206 | COM0  |       | 7007 | 256 | SEG45 |       | 3338    |

| 157 | COM90  | 225   |      | 207 | NC    |       | 6957 | 257 | SEG46 |       | 3263    |

| 158 | COM89  | 175   |      | 208 | NC    |       | 6907 | 258 | SEG47 |       | 3188    |

| 159 | COM88  | 125   |      | 209 | NC    |       | 6857 | 259 | SEG48 |       | 3113    |

| 160 | COM83  | 75    |      | 210 | NC    |       | 6807 | 260 | SEG49 |       | 3038    |

| 161 | COM82  | 25    |      | 211 | SEG0  |       | 6713 | 261 | SEG50 |       | 2963    |

| 162 | COM81  | -25   |      | 212 | SEG1  |       | 6638 | 262 | SEG51 |       | 2888    |

| 163 | COM80  | -75   |      | 213 | SEG2  |       | 6563 | 263 | SEG52 |       | 2813    |

| 164 | COM75  | -125  |      | 214 | SEG3  |       | 6488 | 264 | SEG53 |       | 2738    |

| 165 | COM74  | -175  |      | 215 | SEG4  |       | 6413 | 265 | SEG54 |       | 2663    |

| 166 | COM73  | -225  |      | 216 | SEG5  |       | 6338 | 266 | SEG55 |       | 2588    |

| 167 | COM72  | -275  |      | 217 | SEG6  |       | 6263 | 267 | SEG56 |       | 2513    |

| 168 | COM67  | -325  |      | 218 | SEG7  |       | 6188 | 268 | SEG57 |       | 2438    |

| 169 | COM66  | -375  |      | 219 | SEG8  |       | 6113 | 269 | SEG58 |       | 2363    |

| 170 | COM65  | -425  |      | 220 | SEG9  |       | 6038 | 270 | SEG59 |       | 2288    |

| 171 | COM64  | -475  |      | 221 | SEG10 |       | 5963 | 271 | SEG60 |       | 2213    |

| 172 | COM59  | -524  |      | 222 | SEG11 |       | 5888 | 272 | SEG61 |       | 2138    |

| 173 | COM58  | -574  |      | 223 | SEG12 |       | 5813 | 273 | SEG62 |       | 2063    |

| 174 | COM57  | -624  |      | 224 | SEG13 |       | 5738 | 274 | SEG63 |       | 1988    |

| 175 | COM56  | -674  |      | 225 | SEG14 |       | 5663 | 275 | SEG64 |       | 1913    |

| 176 | COM51  | -724  |      | 226 | SEG15 |       | 5588 | 276 | SEG65 |       | 1838    |

| 177 | COM50  | -774  |      | 227 | SEG16 |       | 5513 | 277 | SEG66 |       | 1763    |

| 178 | COM49  | -824  |      | 228 | SEG17 |       | 5438 | 278 | SEG67 |       | 1688    |

| 179 | COM48  | -874  |      | 229 | SEG18 |       | 5363 | 279 | SEG68 |       | 1613    |

| 180 | COM43  | -924  |      | 230 | SEG19 |       | 5288 | 280 | SEG69 |       | 1538    |

| 181 | COM42  | -974  |      | 231 | SEG20 |       | 5213 | 281 | SEG70 |       | 1463    |

| 182 | COM41  | -1024 |      | 232 | SEG21 |       | 5138 | 282 | SEG71 |       | 1388    |

| 183 | COM40  | -1074 |      | 233 | SEG22 |       | 5063 | 283 | SEG72 |       | 1313    |

| 184 | COM35  | -1124 |      | 234 | SEG23 |       | 4988 | 284 | SEG73 |       | 1238    |

| 185 | COM34  | -1174 |      | 235 | SEG24 |       | 4913 | 285 | SEG74 |       | 1163    |

| 186 | NC     | -1224 | •    | 236 | SEG25 |       | 4838 | 286 | SEG75 |       | 1088    |

| 187 | NC     | -1350 | 7956 | 237 | SEG26 |       | 4763 | 287 | SEG76 |       | 1013    |

| 188 | NC     |       | 7906 | 238 | SEG27 |       | 4688 | 288 | SEG77 |       | 938     |

| 189 | COM33  |       | 7856 | 239 | SEG28 |       | 4613 | 289 | SEG78 |       | 863     |

| 190 | COM32  |       | 7806 | 240 | SEG29 |       | 4538 | 290 | SEG79 |       | 788     |

| 191 | COM27  |       | 7756 | 241 | SEG30 |       | 4463 | 291 | SEG80 |       | 713     |

| 192 | COM26  |       | 7706 | 242 | SEG31 |       | 4388 | 292 | SEG81 |       | 638     |

| 193 | COM25  |       | 7656 | 243 | SEG32 |       | 4313 | 293 | SEG82 |       | 563     |

| 194 | COM24  |       | 7606 | 244 | SEG33 |       | 4238 | 294 | SEG83 |       | 488     |

| 195 | COM19  |       | 7556 | 245 | SEG34 |       | 4163 | 295 | SEG84 |       | 413     |

| 196 | COM18  |       | 7506 | 246 | SEG35 |       | 4088 | 296 | SEG85 |       | 338     |

| 197 | COM17  |       | 7457 | 247 | SEG36 |       | 4013 | 297 | SEG86 |       | 263     |

| 198 | COM16  |       | 7407 | 248 | SEG37 |       | 3938 | 298 | SEG87 |       | 188     |