### TMS320VC5503/5507/5509 DSP Real-Time Clock (RTC) Reference Guide

Literature Number: SPRU594B June 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

### Preface

### **Read This First**

#### About This Manual

This manual describes the features and operation of the real-time clock (RTC) that is on the TMS320VC5503, TMS320VC5507, TMS320VC5509, and TMS320VC5509A digital signal processors (DSPs) in the TMS320C55 $x^{TM}$  (C55 $x^{TM}$ ) DSP generation.

#### Notational Conventions

This document uses the following conventions:

In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers often are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form:

0100b

- ☐ If a signal or pin is active low, it has an overbar. For example, the RESET signal is active low.

- Bits and signals are sometimes referenced with the following notations:

| Notation      | Description                  | Example                                           |

|---------------|------------------------------|---------------------------------------------------|

| Register(n-m) | Bits n through m of Register | R(3–0) represents bits 3 through 0 of register R. |

| Bus[n:m]      | Signals n through m of Bus   | A[21:1] represents signals 21 through 1 of bus A. |

The following terms are used to name portions of data:

| Term | Description           | Example                      |

|------|-----------------------|------------------------------|

| LSB  | Least significant bit | In R(7–0), bit 0 is the LSB. |

| MSB  | Most significant bit  | In R(7–0), bit 7 is the MSB. |

SPRU594B

#### **Related Documentation From Texas Instruments**

The following documents describe the C55x devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **TMS320VC5503 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS245) describes the features of the TMS320VC5503 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- *TMS320VC5507 Fixed-Point Digital Signal Processor Data Manual* (literature number SPRS244) describes the features of the TMS320VC5507 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5509 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS163) describes the features of the TMS320VC5509 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5509A Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS205) describes the features of the TMS320VC5509A fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320C55x Technical Overview** (literature number SPRU393) introduces the TMS320C55x DSPs, the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

- *TMS320C55x DSP CPU Reference Guide* (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x DSPs.

- *TMS320C55x DSP Peripherals Overview Reference Guide* (literature number SPRU317) introduces the peripherals, interfaces, and related hardware that are available on TMS320C55x DSPs.

- **TMS320C55x DSP Algebraic Instruction Set Reference Guide** (literature number SPRU375) describes the TMS320C55x DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- *TMS320C55x DSP Mnemonic Instruction Set Reference Guide* (literature number SPRU374) describes the TMS320C55x DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C/C++ Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x C/C++ Compiler. This C/C++ compiler accepts ISO standard C and C++ source code and produces assembly language source code for TMS320C55x devices.

- **TMS320C55x Assembly Language Tools User's Guide** (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

- **TMS320C55x DSP Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x DSPs and explains how to write code that uses special features and instructions of the DSPs.

#### Trademarks

TMS320, TMS320C5000, TMS320C55x, and C55x are trademarks of Texas Instruments.

Trademarks are the property of their respective owners.

## **Contents**

| Intro |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.2   | Real-Time Clock Reference Clock Source                                                                                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Using | g the Real-Time Clock Time and Calendar Registers                                                                                                                      | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1   | Time/Calendar Data Format                                                                                                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.2   | 12-Hour and 24-Hour Modes                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.3   | Reading and Writing the Time/Calendar Registers                                                                                                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 2.3.1 How to Set the Time/Calendar                                                                                                                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 2.3.2 How to Read the Time/Calendar Using the SET Bit                                                                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 2.3.3 How to Read the Time/Calendar Without Using the SET Bit                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Usind | the Real-Time Clock Time and Calendar Alarms                                                                                                                           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3   | ,                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.6   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.7   | Examples of Time/Calendar Alarms Settings                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Real- | Time Clock Interrupt Requests                                                                                                                                          | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | • •                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4   | Update-Ended Interrupt Request                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Real- | Time Clock Update Cycle                                                                                                                                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Powe  | er, Emulation, and Reset Considerations                                                                                                                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.1   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.2   |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.3   | Real-Time Clock After a DSP Reset                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 1.1<br>1.2<br>Using<br>2.1<br>2.2<br>2.3<br>Using<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>Real-<br>4.1<br>4.2<br>4.3<br>4.4<br>Real-<br>Powe<br>6.1<br>6.2 | 1.2  Real-Time Clock Reference Clock Source    Using the Real-Time Clock Time and Calendar Registers    2.1  Time/Calendar Data Format    2.2  12-Hour and 24-Hour Modes    2.3  Reading and Writing the Time/Calendar Registers    2.3.1  How to Set the Time/Calendar    2.3.2  How to Read the Time/Calendar    2.3.3  How to Read the Time/Calendar Using the SET Bit    2.3.4  How to Read the Time/Calendar Without Using the SET Bit    2.3.3  How to Read the Time/Calendar Alarms    3.1  Time/Calendar Alarm Data Format    3.2  Day Alarm    3.3  Hours Alarm    3.4  Minutes Alarm    3.5  Seconds Alarm    3.6  Reading and Writing the Time/Calendar Alarm Registers    3.7  Examples of Time/Calendar Alarms Settings    Real-Time Clock Interrupt Requests |

#### Contents

| 7  | Real-  | Time Clock Registers                                    | 27 |

|----|--------|---------------------------------------------------------|----|

|    | 7.1    | Seconds Register (RTCSEC)                               | 27 |

|    | 7.2    | Seconds Alarm Register (RTCSECA)                        | 28 |

|    | 7.3    | Minutes Register (RTCMIN)                               | 28 |

|    | 7.4    | Minutes Alarm Register (RTCMINA)                        | 29 |

|    | 7.5    | Hours Register (RTCHOUR)                                |    |

|    | 7.6    | Hours Alarm Register (RTCHOURA)                         | 30 |

|    | 7.7    | Day of the Week and Day Alarm Register (RTCDAYW)        |    |

|    | 7.8    | Day of the Month (Date) Register (RTCDAYM)              | 32 |

|    | 7.9    | Month Register (RTCMONTH)                               | 33 |

|    | 7.10   | Year Register (RTCYEAR)                                 | 33 |

|    | 7.11   | Interrupt Registers                                     |    |

|    |        | 7.11.1 Periodic Interrupt Selection Register (RTCPINTR) | 34 |

|    |        | 7.11.2 Interrupt Enable Register (RTCINTEN)             | 35 |

|    |        | 7.11.3 Interrupt Flag Register (RTCINTFL)               |    |

| Re | vision | History                                                 | 38 |

# Figures

| 1  | Real-Time Clock Block Diagram                    | 12 |

|----|--------------------------------------------------|----|

| 2  | Seconds Register (RTCSEC)                        | 27 |

| 3  | Seconds Alarm Register (RTCSECA)                 | 28 |

| 4  | Minutes Register (RTCMIN)                        | 28 |

| 5  | Minutes Alarm Register (RTCMINA)                 | 29 |

| 6  | Hours Register (RTCHOUR)                         | 29 |

| 7  | Hours Alarm Register (RTCHOURA)                  | 30 |

| 8  | Day of the Week and Day Alarm Register (RTCDAYW) | 32 |

| 9  | Day of the Month (Date) Register (RTCDAYM)       | 32 |

| 10 | Month Register (RTCMONTH)                        | 33 |

| 11 | Year Register (RTCYEAR)                          | 33 |

| 12 | Periodic Interrupt Selection Register (RTCPINTR) | 34 |

| 13 | Interrupt Enable Register (RTCINTEN)             | 35 |

| 14 | Interrupt Flag Register (RTCINTFL)               | 37 |

|    |                                                  |    |

## **Tables**

| 1  | Real-Time Clock Signal Descriptions 1                         | 3  |

|----|---------------------------------------------------------------|----|

| 2  | Time/Calendar Registers 1                                     | 4  |

| 3  | Time/Calendar Alarm Registers 1                               | 8  |

| 4  | Real-Time Clock Alarm Example Settings 2                      | 20 |

| 5  | RTC Periodic Interrupt Rates Based on RATE Bits 2             | 23 |

| 6  | Real-Time Clock Registers 2                                   | 27 |

| 7  | Seconds Register (RTCSEC) Field Values 2                      | 27 |

| 8  | Seconds Alarm Register (RTCSECA) Field Values                 | 28 |

| 9  | Minutes Register (RTCMIN) Field Values 2                      | 28 |

| 10 | Minutes Alarm Register (RTCMINA) Field Values 2               | 29 |

| 11 | Hours Register (RTCHOUR) Field Values 2                       | 29 |

| 12 | Hours Alarm Register (RTCHOURA) Field Values                  | 31 |

| 13 | Day of the Week and Day Alarm Register (RTCDAYW) Field Values | 32 |

| 14 | Day of the Month (Date) Register (RTCDAYM) Field Values       | 32 |

| 15 | Month Register (RTCMONTH) Field Values                        | 33 |

| 16 | Year Register (RTCYEAR) Field Values 3                        | 33 |

| 17 | Periodic Interrupt Selection Register (RTCPINTR) Field Values | 34 |

| 18 | Interrupt Enable Register (RTCINTEN) Field Values             | 36 |

| 19 | Interrupt Flag Register (RTCINTFL) Field Values               | 37 |

|    |                                                               |    |

This document describes the real-time clock (RTC) available on the TMS320VC5503, TMS320VC5507, TMS320VC5509 and TMS320VC5509A DSPs. The RTC provides a time reference and the capability to generate time-based alarms to interrupt the DSP.

#### 1 Introduction to the Real-Time Clock (RTC)

The real-time clock (RTC) provides the following features:

- 100-year calendar up to year 2099

- Counts seconds, minutes, hours, day of the week, date, month, and year with leap year compensation

- Binary-coded-decimal (BCD) representation of time, calendar, and alarm

- 12-hour clock mode (with AM and PM) or 24-hour clock mode

- Second, minute, hour, day, or week alarm interrupt

- Update cycle interrupt

- Periodic interrupt

- Single interrupt to the DSP CPU

- Supports external 32.768-kHz crystal or external clock source of the same frequency

- Separate isolated power supply

The RTC provides a time reference to an application running on the DSP. The current date and time is tracked in a set of counter registers that update once per second. The time can be represented in 12-hour or 24-hour mode. The calendar and time registers are buffered during reads and writes so that updates do not interfere with the accuracy of the time and date. For information on how to set the time and date, see section 2.3 on page 15.

Alarms are available to interrupt the DSP CPU at a particular time, or at periodic time intervals, such as once per minute or once per day. In addition, the RTC can interrupt the CPU every time the calendar and time registers are updated, or at programmable periodic intervals. For information on how to set and use alarms, see section 3 on page 18.

The clock reference for the RTC is an external 32.768-kHz crystal (connected between signals RTCINX1 and RTCINX2) or an external clock source of the same frequency. The RTC also has a separate power supply that is isolated from the rest of the DSP. When the DSP is without power, the RTC can remain powered to preserve the current time and calendar information.

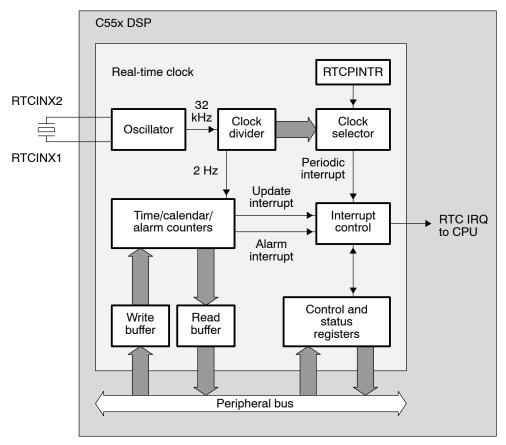

Figure 1 shows a block diagram of the RTC. Table 1 lists and describes the signals.

Figure 1. Real-Time Clock Block Diagram

| Table 1. Real-Time Clock Signal Des | scriptions |

|-------------------------------------|------------|

|-------------------------------------|------------|

| Name    | I/O    | Signal Descriptions                                                                                                                                                                                                                              |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTCINX1 | Input  | RTC time base input signal<br>RTCINX1 can either be driven with a 32.768-kHz reference clock, or RTCINX1<br>and RTCINX2 and be connected to an external crystal. This signal is the input to<br>the RTC internal oscillator used by the crystal. |

| RTCINX2 | Output | RTC time base output signal<br>RTCINX2 is the output from the RTC internal oscillator used by the crystal. If a<br>crystal is not used as the time base for RTCINX1, RTCINX2 should be left<br>unconnected.                                      |

#### 1.1 Real-Time Clock Power Supply

The RTC has a power supply that is isolated from the rest of the DSP. This allows the RTC to continue to run while the rest of the DSP is not powered. In this state, the RTC time and calendar counters continue to run, but the RTC is unable to cause interrupts to the DSP since the DSP is not powered. The configuration of the alarm registers is also maintained as long as the RTC is powered. Separate power supply pins for the RTC are provided on the device package. For specific information about the RTC power supply connections, see the data manual for the DSP being used.

#### 1.2 Real-Time Clock Reference Clock Source

The RTC uses an external 32.768-kHz reference clock as its basis for keeping time.

The source for the RTC reference clock may be provided by a crystal or by an external clock source. The RTC has an internal oscillator to support operation with a crystal. The crystal is connected between pins RTCINX1 and RTCINX2. RTCINX1 is the input to the on-chip oscillator and RTCINX2 is the output from the oscillator back to the crystal. For more information about the RTC crystal connection, see the data manual for the DSP being used.

An external 32.768-kHz clock source may be used instead of a crystal. In this case, the clock source is connected to RTCINX1, and RTCINX2 is left unconnected.

#### 2 Using the Real-Time Clock Time and Calendar Registers

The current time and date are maintained in the RTC time and calendar registers. Information about how to use these registers is in the sections that follow.

#### 2.1 **Time/Calendar Data Format**

The time and calendar data in the RTC is stored as binary-coded decimal (BCD) format. In BCD format, the decimal numbers 0 through 9 are encoded with their binary equivalent. Although most of the time/calendar registers have 4 bits assigned to each BCD digit, some of the register fields are shorter since the range of valid numbers may be limited. For example, only 3 bits are required to represent the day since only BCD numbers 1 though 7 are required.

The summary of the time/calendar registers is shown in Table 2. The alarm registers are interleaved with the time/calendar registers and are not shown in this table. The alarm registers are shown in Table 3. A complete description all RTC registers is available in section 7 (page 27).

| Address (Hex) | Name     | Function                        | Decimal Range | BCD Format                |

|---------------|----------|---------------------------------|---------------|---------------------------|

| 1800h         | RTCSEC   | Seconds                         | 0–59          | 00–59                     |

| 1802h         | RTCMIN   | Minutes 0–59                    |               | 00–59                     |

| 1804h         | RTCHOUR  | 12-hour mode 1–12               |               | 01–12 (AM),<br>81–92 (PM) |

|               |          | 24-hour mode                    | 0–23          | 00–23                     |

| 1806h         | RTCDAYW  | Day of the week<br>(Sunday = 1) | 1–7           | 1–7                       |

| 1807h         | RTCDAYM  | Day of the month (Date) 1-31    |               | 01–31                     |

| 1808h         | RTCMONTH | Month (January = 01)            | 1–12          | 01–12                     |

| 1809h         | RTCYEAR  | Year                            | 0–99          | 00–99                     |

Table 2. Time/Calendar Registers

The RTC Seconds Register (RTCSEC) stores the seconds value of the current time. The minutes register (RTCMIN) stores the minutes value of the current time. The seconds and minutes are encoded BCD values 00 (0000b 0000b) through 59 (0101b 1001b).

The RTC Hours Register (RTCHOUR) stores the hours value of the current time. The hours are encoded BCD values 01 (0000b 0001b) through 12 (0001b 0010b) in 12-hour mode, or 00 (0000b 0000b) through 23 (0010b 0011b) in 24-hour mode. Selection of 12-hour or 24-hour mode is described in section 2.2.

14

The RTC Day of the Week and Day Alarm Register (RTCDAYW) stores the day of the week value of the current date. The DAY field of RTCDAYW is 3 bits and encodes the day of the week as BCD values 1 (001b) through 7 (111b). The days of the week are represented as Sunday (1) though Saturday (7).

The RTC Day of the Month Register (RTCDAYM) stores the day of the month for the current date. The day of the month is encoded as BCD values 01 (0000b 0001b) through 31 (0011b 0001b).

The RTC Month Register (RTCMONTH) stores the month for the current date. The month is encoded as BCD values 01 (0000b 0001b) through 12 (0001b 0010b).

The RTC Year Register (RTCYEAR) stores the year for the current date. The year is encoded as BCD values 00 (0000b 0000b) through 99 (1001b 1001b).

#### 2.2 12-Hour and 24-Hour Modes

The current time can be represented in 12-hour or 24-hour mode by configuring the TM bit in the RTC Interrupt Enable Register (RTCINTEN). When

TM = 0, 12-hour mode is selected. In 12-hour mode, the hours are represented as 1 though 12 and the AMPM bit in RTCHOUR indicates AM or PM. When AMPM = 0, the current time is AM. When AMPM = 1, the current time is PM.

When TM = 1, 24-hour mode is selected and the hours are represented as 0 through 23. In this mode, the AMPM bit has no function and should be cleared.

#### 2.3 Reading and Writing the Time/Calendar Registers

The time/calendar registers are updated every second as the time changes. To protect the accuracy of the time/date contained in these registers, the RTC provides a read buffer and a write buffer for access to the time/calendar register. During a read of the time/calendar registers, the RTC copies the current time/date form the time/calendar registers into the read buffer and the read buffer is isolated form the time/calendar registers. This isolation assures that the CPU reads the time/date present at the time of the read request rather than after the automatic updating. During writes, the desired value of the time/calendar registers. While the CPU is writing to the write buffer, it is isolated from the time/calendar registers, preserving the accuracy of the current time/date.

The SET bit in RTCINTEN controls the isolation of the read and write buffers from the time/calendar registers. When SET = 0, the read and write buffers are directly connected to the time/calendar registers. In this state, the current time/date can be read directly but there is no protection of the read data during an update cycle. In other words, if the RTC updates the current time/date while the CPU is reading the time/calendar registers, an inaccurate time/date could be read. When SET = 1, the time/calendar registers are copied to the read buffer and then the read buffer is isolated form the time/calendar registers. So even if the RTC updates the current time/date, the read value is preserved in the read buffers. Procedures for reading and writing the time/calendar registers are described in the sections that follow.

#### 2.3.1 How to Set the Time/Calendar

To write a new value to the time/calendar registers, use the following procedure:

- Set the SET bit in RTCINTEN to isolate the write buffer from the time/calendar registers.

- Write the desired time and date to the time/calendar registers (RTCSEC, RTCMIN, RTCHOUR, RTCDAYW, RTCDAYM, RTCMONTH and RTCYEAR). Since SET = 1, these values actually go to the write buffer.

- Clear the SET bit to copy the write buffer values to the time/calendar registers.

#### 2.3.2 How to Read the Time/Calendar Using the SET Bit

To read the current time/date using the SET bit, use the following procedure:

- Set the SET bit in RTCINTEN to copy the current time/date into the read buffer and isolate the read buffer from the time/calendar registers.

- Read the current time and date from the time/calendar registers (RTCSEC, RTCMIN, RTCHOUR, RTCDAYW, RTCDAYM, RTCMONTH and RTCYEAR). Since SET = 1, these values are actually being read from the read buffer.

- Clear the SET bit reconnect the read buffer to the time/calendar registers.

This method will provide the time/date that was current when the SET bit was set and prevents reading an incorrect time due to an RTC update.

#### 2.3.3 How to Read the Time/Calendar Without Using the SET Bit

To read the current time/date without using the SET bit, use the following procedure:

- Leave the SET bit cleared.

- Read the RTCSEC for the seconds value of the current time/date.

- Read the remaining time/calendar register values (RTCMIN, RTCHOUR, RTCDAYW, RTCDAYM, RTCMONTH and RTCYEAR) of the current time/date.

- Read RTCSEC again and compare to the previous value. If both values are the same, an RTC update did not occur while the other registers were being read and the all of the values read represent the current time. If the seconds have changed, this indicates an RTC update occurred while the registers were being read and the process should be repeated.

This method provides the time/date that was current when the registers were read.

#### **3** Using the Real-Time Clock Time and Calendar Alarms

Alarms can be configured to interrupt the CPU at any of the following intervals:

- On a specific seconds value, or every second

- On a specific minutes value, or every minute

- On a specific hours value, or every hour

- On a specific day of the week value, or every day

The time/calendar alarm registers control the setting of alarms. Information about how to use these registers is in the sections that follow. The alarms can also be configured to generate an interrupt to the CPU. The operation of the alarm interrupt is described in section 4.3 (page 24).

#### 3.1 Time/Calendar Alarm Data Format

The time and calendar alarm data in the RTC is stored as binary-coded decimal (BCD) format. In BCD format, the decimal numbers 0 through 9 are encoded with their binary equivalent. Although most of the time/calendar alarm registers have 4 bits assigned to each BCD digit, some of the register field lengths may differ to accommodate the desired function.

The summary of the time/calendar alarm registers is shown in Table 3. The time/calendar registers are interleaved with the alarm registers and are not shown in this table. The time/calendar registers are shown in Table 2. A complete description of all RTC registers is available in section 7 (page 27).

| Address (Hex) | Name                                           | Function              | Decimal Range | BCD Format  |

|---------------|------------------------------------------------|-----------------------|---------------|-------------|

| 1801h         | RTCSECA                                        | Seconds alarm         | 0–59          | 00–59       |

|               |                                                |                       | don't care    | C0-FF       |

| 1803h         | RTCMINA                                        | Minutes alarm         | 0–59          | 00–59       |

|               |                                                |                       | don't care    | C0-FF       |

| 1805h         | RTCHOURA 12-hour mode alarm 1–12<br>don't care | 12-hour mode alarm    | 1–12          | 01–12 (AM), |

|               |                                                |                       |               | 81–92 (PM)  |

|               |                                                | don't care            | C0-FF         |             |

|               |                                                | 24-hour mode alarm    | 0–23          | 00–23       |

|               |                                                |                       | don't care    | C0-FF       |

| 1806h         | RTCDAYW                                        | Day of the week alarm | 1–7           | 1–7         |

|               |                                                | (Sunday = 1)          | don't care    | 8–F         |

Table 3. Time/Calendar Alarm Registers

#### 3.2 Day Alarm

The RTC Day of the Week and Day Alarm Register (RTCDAYW) stores the day of the week value of the desired alarm. The DAR field of RTCDAYW is 4 bits. Bits 6-4 encode the desired day for the alarm as BCD values 1 (001b) through 7 (111b). The days of the week are represented as Sunday (1) though Saturday (7).

Bit 7 represents a "don't care" condition and causes an alarm to occur every day. Therefore, while DAR values 0h through 7h cause an alarm to occur on the specified day of the week, DAR values 8h through Fh cause an alarm to occur every day.

#### 3.3 Hours Alarm

The RTC Hours Alarm Register (RTCHOURA) stores the hour value of the desired alarm. The hours are encoded BCD values 01 (0000b 0001b) through 12 (0001b 0010b) in 12-hour mode, or 00 (0000b 0000b) through 23 (0010b 0011b) in 24-hour mode. Selection of 12-hour or 24-hour mode is described in section 2.2 (page 15).

In 12-hour mode (TM = 0 in RTCINTEN), the HAR field contains the hour of the desired alarm time and the AMPM bit indicates whether the alarm should occur in the morning or evening. When AMPM = 0, the value in the HAR field represents AM. When AMPM = 1, the value in the HAR field represents PM.

In 24-hour mode (TM = 1 in RTCINTEN), the HAR field contains the hour of the desired alarm time and the AMPM bit should be cleared.

An alarm can be generated every hour by setting bits 7 and 6 in RTCHOURA. In this case, the remaining bits in the register do not affect the alarm.

#### 3.4 Minutes Alarm

The RTC Minutes Alarm Register (RTCMINA) stores the minute value of the desired alarm. The minutes are encoded BCD values 00 (0000b 0000b) through 59 (0101b 1001b).

An alarm can be generated every minute by setting bits 7 and 6 in RTCMINA. In this case, the remaining bits in the register to not affect the alarm.

#### 3.5 Seconds Alarm

The RTC Seconds Alarm Register (RTCSECA) stores the seconds value of the desired alarm. The seconds are encoded BCD values 00 (0000b 0000b) through 59 (0101b 1001b).

The seconds alarm register cannot be used to generate an alarm every second, but the update-ended interrupt can. The update-ended interrupt is described in section 4.4 (page 24).

#### 3.6 Reading and Writing the Time/Calendar Alarm Registers

To write a new value to the time/calendar alarm registers, use the following procedure:

- Set the SET bit in RTCINTEN to isolate the write buffer from the time/calendar alarm registers.

- Write the desired alarm values to the time/calendar alarm registers (RTCSECA, RTCMINA, RTCHOURA, and RTCDAYW). Since SET = 1, these values actually go to the write buffer.

- Clear the SET bit to copy the write buffer values to the time/calendar alarm registers.

The time/calendar alarm registers can be read directly without using the SET bit since they do not change when the RTC updates the current time/date.

#### 3.7 Examples of Time/Calendar Alarms Settings

Some examples of various alarm settings are shown in Table 4. Entries marked "–" indicate that the "don't care" value for that particular register should be used. A complete description of the RTC registers and their functions is provided in section 7 (page 27).

| Alarm occurs                                         | тм | DAR in<br>RTCDAYW | HAR in<br>RTCHOURA | AMPM in<br>RTCHOURA | MAR in<br>RTCMINA | SAR in<br>RTCSECA |

|------------------------------------------------------|----|-------------------|--------------------|---------------------|-------------------|-------------------|

| Every Monday at 3:19:46 AM<br>(12-hour mode)         | 0  | 2 (Monday)        | 3                  | 0                   | 19                | 46                |

| Every Monday at 3:19:46 PM (12-hour mode)            | 0  | 2 (Monday)        | 3                  | 1                   | 19                | 46                |

| Every Monday at 3:19:46 PM<br>(24-hour mode)         | 1  | 2 (Monday)        | 15                 | 0                   | 19                | 46                |

| Every day at 3:19:46 PM                              | 0  | _                 | 3                  | 1                   | 19                | 46                |

| Every hour on Mondays at xx:19:46                    | -  | 2 (Monday)        | -                  | _                   | 19                | 46                |

| Every minute on Mondays at 3:xx:46 PM (24-hour mode) | 1  | 2 (Monday)        | 15                 | 0                   | _                 | 46                |

| Every minute at xx:xx:46                             | 1  | -                 | -                  | 0                   | -                 | 46                |

| Table 4. | Real-Time Clock Alarm Example Settings |

|----------|----------------------------------------|

|----------|----------------------------------------|

#### 4 Real-Time Clock Interrupt Requests

The RTC provides the ability to interrupt the CPU based on three events: a periodic interrupt, an alarm interrupt, or an update-ended interrupt. Although three interrupt sources are available, the RTC makes a single interrupt request to the CPU. Specific information about using each of the interrupt types is in the sections that follow.

#### 4.1 Interrupt Enable and Flag Bits

Three bits (PIE, AIE, and UIE) in the interrupt enable register (RTCINTEN) enable the interrupts. PIE enables the periodic interrupt, AIE enables the alarm interrupt, and UIE enables the update-ended interrupt. Writing a logic 1 to an interrupt enable bit allows that interrupt to generate an RTC interrupt request to the CPU when the event occurs. If an RTC interrupt flag is already set when an interrupt is enabled, the RTC interrupt to the CPU occurs immediately, although the interrupt initiating the event may have occurred much earlier. Pending interrupts should be cleared before first enabling new interrupts.

When an interrupt event occurs, the corresponding flag bit (PF, AF, or UF) is set in the interrupt flag register (RTCINTFL). PF is associated with the periodic interrupt, AF is associated with the alarm interrupt, and UF is associated with the update-ended interrupt. These flag bits are set independent of the state of the corresponding enable bit in RTCINTEN. The flag bit can be used in a polling mode without enabling the corresponding enable bits.

If one of the three flag bits becomes active and the corresponding enable bit is set, an RTC interrupt to the CPU occurs. The RTC interrupt is asserted as long as at least one of the three interrupt flag bits and enable bits are set. The IRQF bit in RTCINTFL is set to 1 when the RTC interrupt to the CPU is asserted. The IRQF bit indicates that one or more interrupts have been initiated by the RTC. When an interrupt occurs from the RTC, the source of the interrupt can be determined by reading the flag bits in RTCINTFL.

#### Note:

On the TMS320VC5503/5507/5509 and TMS320VC5509A DSPs, the RTC interrupt is shared with external interrupt 4 (INT4) in interrupt flag register 1 (bit 3 in IFR1). The presence of an interrupt flag in this bit indicates that either INT4 or the RTC interrupt has occurred. The source of an RTC interrupt can be identified by reading RTCINTFL. If no RTC interrupt flags are present, the interrupt source was INT4.

This interrupt should not be used for both INT4 and RTC at the same time because some interrupt events may be missed if both interrupt sources occur near the same time. In this case, when the interrupt service is entered, the CPU clears the interrupt flag in the CPU. After the return from the interrupt service routine, the second interrupt source is not serviced since the interrupt flag in the CPU was cleared.

#### 4.2 Periodic Interrupt Request

The periodic interrupt causes the RTC to make an interrupt request to the CPU periodically from once every minute to once every 122  $\mu$ s. The periodic interrupt rate is selected using the RATE bits in the periodic interrupt selection register (RTCPINTR); see Table 5. Changing bits 3-0 of the RATE bits affects the periodic interrupt rate. When bit 4 of the RATE bits is set to 1, the periodic interrupt is asserted every minute regardless of the other RATE bit values. The minute interrupt is triggered when the seconds register is changed from 59 to 00. The periodic interrupts are enabled by the PIE bit in RTCINTEN.

| RTCPINTR Bits<br>RATE(4-0) | Periodic Interrupt Rate       |

|----------------------------|-------------------------------|

| 00000                      | No interrupt                  |

| 00001                      | Reserved                      |

| 00010                      | Reserved                      |

| 00011                      | 122.070 μs (8192 per second)  |

| 00100                      | 244.141 μs (4096 per second)  |

| 00101                      | 488.281 μs (2048 per second)  |

| 00110                      | 976.5625 μs (1024 per second) |

| 00111                      | 1.953125 ms (512 per second)  |

| 01000                      | 3.90625 ms (256 per second)   |

| 01001                      | 7.8125 ms (128 per second)    |

| 01010                      | 15.625 ms (64 per second)     |

| 01011                      | 31.25 ms (32 per second)      |

| 01100                      | 62.5 ms (16 per second)       |

| 01101                      | 125 ms (8 per second)         |

| 01110                      | 250 ms (4 per second)         |

| 01111                      | 500 ms (2 per second)         |

| 1xxxx                      | 1 minute                      |

#### Table 5. RTC Periodic Interrupt Rates Based on RATE Bits

To use the RTC periodic interrupt:

- Select the desired interrupt rate using by configuring the RATE bits in RTCPINTR.

- **D** Enable the RTC periodic interrupt by setting the PIE bit in RTCINTEN.

- Enable the RTC interrupt in the CPU interrupt enable register 1 (IER1).

When the periodic interrupt occurs, the PF and IRQF flags in RTCINTFL are set and the RTC interrupt is sent to the CPU.

#### 4.3 Alarm Interrupt Request

The RTC alarm interrupt can be used to generate an interrupt to the CPU at specific times. The alarm interrupt occurs when the alarm time programmed in the RTC alarm registers (RTCSECA, RTCMINA, RTCHOURA, and RTCDAYW) match the current time. For information about programming an alarm time, see section 3 on page 18.

To use the RTC alarm interrupt:

- Select the desired alarm time by configuring the RTC alarm registers.

- Enable the RTC alarm interrupt by setting the AIE bit in RTCINTEN.

- Enable the RTC interrupt in the CPU interrupt enable register 1 (IER1).

When the alarm interrupt occurs, the AF and IRQF flags in RTCINTFL are set and the RTC interrupt is sent to the CPU.

#### 4.4 Update-Ended Interrupt Request

The RTC update-ended interrupt can be used to generate an interrupt to the CPU after each update of the RTC time/calendar registers. For more detailed information on the operation of the RTC update cycle, see section 5 on page 25.

To use the RTC update-ended interrupt:

- Enable the RTC update-ended interrupt by setting the UIE bit in RTCINTEN.

- Enable the RTC interrupt in the CPU interrupt enable register 1 (IER1).

When the update-ended interrupt occurs, the UF and IRQF flags in RTCINTFL are set and the RTC interrupt is sent to the CPU.

#### 5 Real-Time Clock Update Cycle

The RTC executes an update cycle once per second to update the current time in the time/calendar registers. This update occurs regardless of the SET bit value in the interrupt enable register (RTCINTEN). When the SET bit is set to 1, the time, calendar, and alarm registers are double buffered and become separate from the actual time, calendar, and alarm registers. This allows the RTC to maintain accuracy independent of reading or writing to the buffers. The update cycle also compares each alarm register with the corresponding time register. These comparisons are done to determine when to trigger an alarm.

The RTC provides two mechanisms to indicate when the time/calendar registers are updated:

- ☐ The first method uses the update-ended interrupt enable (UIE) bit in RTCINTEN. If the update-ended interrupt is enabled, an interrupt occurs after every update cycle. When the interrupt occurs, the update flag (UF) is set, indicating that an update has just been completed.

- The second method uses the update-in-progress (UIP) bit in the periodic interrupt selection register (RTCPINTR) to determine if the update cycle is in progress. When UIP goes high, an update occurs within 244 μs. When UIP returns low again, the update has been completed.

#### 6 Power, Emulation, and Reset Considerations

The following sections describe how the RTC is affected by DSP low power modes (idle configurations), emulation breakpoints and a DSP reset.

## 6.1 Real-Time Clock Response to Low Power Modes (Idle Configurations)

The DSP is divided into idle domains that can be programmed to be idle or active. The state of all domains is called the idle configuration. The RTC runs on its own external clock source and is not affected by any of the DSP idle domains.

#### 6.2 Emulation Modes of the Real-Time Clock

The RTC always continues to run regardless of the state (running/halted) of the emulation debugger software.

#### 6.3 Real-Time Clock After a DSP Reset

A DSP reset resets only certain register fields in the RTC. The time/calendar and alarm registers are not affected by a DSP reset. For detailed information on how each RTC register responds to a DSP reset, see the register descriptions in section 7.

#### 7 Real-Time Clock Registers

The RTC registers are listed in Table 6 and described in detail in the sections that follow.

| Address     | Name     | Description                               | See       |

|-------------|----------|-------------------------------------------|-----------|

| 1800h       | RTCSEC   | Seconds Register                          | This page |

| 1801h       | RTCSECA  | Seconds Alarm Register                    | Page 28   |

| 1802h       | RTCMIN   | Minutes Register                          | Page 28   |

| 1803h       | RTCMINA  | Minutes Alarm Register                    | Page 29   |

| 1804h       | RTCHOUR  | Hours Register                            | Page 29   |

| 1805h       | RTCHOURA | Hours Alarm Register                      | Page 30   |

| 1806h       | RTCDAYW  | Day of the Week and Day Alarm<br>Register | Page 32   |

| 1807h       | RTCDAYM  | Day of the Month (Date) Register          | Page 32   |

| 1808h       | RTCMONTH | Month Register                            | Page 33   |

| 1809h       | RTCYEAR  | Year Register                             | Page 33   |

| 180Ah       | RTCPINTR | Periodic Interrupt Selection Register     | Page 34   |

| 180Bh       | RTCINTEN | Interrupt Enable Register                 | Page 35   |

| 180Ch       | RTCINTFL | Interrupt Flag Register                   | Page 37   |

| 180Dh-1BFFh | -        | Reserved                                  | _         |

Table 6. Real-Time Clock Registers

#### 7.1 Seconds Register (RTCSEC)

Figure 2. Seconds Register (RTCSEC)

| 7     | 0 |

|-------|---|

| SEC   |   |

| R/W–U |   |

Legend: R = Read; W = Write; -U = Value unchanged by reset

#### Table 7. Seconds Register (RTCSEC) Field Values

| Bit | Field | BCD<br>Value | Description                                                                     |

|-----|-------|--------------|---------------------------------------------------------------------------------|

| 7–0 | SEC   | 00–59        | Seconds select bits. This BCD value sets the seconds value of the current time. |

\_

#### 7.2 Seconds Alarm Register (RTCSECA)

Figure 3. Seconds Alarm Register (RTCSECA)

| 7     | 0 |

|-------|---|

| SAR   |   |

| R/W–U |   |

**Legend:** R = Read; W = Write; -U = Value unchanged by reset

#### Table 8. Seconds Alarm Register (RTCSECA) Field Values

| Bit | Field | BCD<br>Value | Description                                                                         |

|-----|-------|--------------|-------------------------------------------------------------------------------------|

| 7–0 | SAR   | 00–59        | Seconds alarm select bits. This BCD value sets the seconds value of the alarm time. |

### 7.3 Minutes Register (RTCMIN)

Figure 4. Minutes Register (RTCMIN)

| 7     | 0 |

|-------|---|

| MIN   |   |

| R/W–U |   |

Legend: R = Read; W = Write; -U = Value unchanged by reset

#### Table 9. Minutes Register (RTCMIN) Field Values

| Bit | Field | BCD<br>Value | Description                                                                     |

|-----|-------|--------------|---------------------------------------------------------------------------------|

| 7–0 | MIN   | 00–59        | Minutes select bits. This BCD value sets the minutes value of the current time. |

### 7.4 Minutes Alarm Register (RTCMINA)

Figure 5. Minutes Alarm Register (RTCMINA)

| 7 |       | 0 |

|---|-------|---|

|   | MAR   |   |

|   | R/W–U |   |

Legend: R = Read; W = Write; -U = Value unchanged by reset

| Table 10. | Minutes Alarm Register (RTCMINA) Field Values |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Bit | Field | BCD<br>Value | Description                                                                                                      |

|-----|-------|--------------|------------------------------------------------------------------------------------------------------------------|

| 7–0 | MAR   | 00–59        | Minutes alarm select bits. This BCD value sets the minute of the alarm time.                                     |

|     |       |              | When bits 7 and 6 are set to 1, a "don't care" condition is set and the RTC generates an interrupt every minute. |

#### 7.5 Hours Register (RTCHOUR)

Figure 6. Hours Register (RTCHOUR)

| 7     | 0     |

|-------|-------|

| AMPM  | HR    |

| R/W-0 | R/W–U |

**Legend:** R = Read; W = Write; -n = Value after reset; -U = Value unchanged by reset

| Table 11. | Hours Register | (RTCHOUR) Field Values |

|-----------|----------------|------------------------|

|           |                |                        |

|     |       | BCD   |                     |

|-----|-------|-------|---------------------|

| Bit | Field | Value | Description         |

| 7   | AMPM  |       | AM/PM select bit.   |

|     |       | 0     | Time is set for AM. |

|     |       | 1     | Time is set for PM. |

| Bit | Field | BCD<br>Value | Description                                                                                                                                                  |

|-----|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–0 | HR    |              | Hours select bits. This BCD value sets the hour of the time.                                                                                                 |

|     |       |              | For 12-hour mode (TM = 0 in RTCINTEN):                                                                                                                       |

|     |       | 01–12        | This BCD value sets the hour of the current time in conjunction with the AMPM bit. For AM, AMPM bit must be cleared to 0; for PM, AMPM bit must be set to 1. |

|     |       |              | For 24-hour mode (TM = 1 in RTCINTEN):                                                                                                                       |

|     |       | 00–23        | This BCD value sets the hour of the current time. The AMPM bit must be cleared to 0.                                                                         |

Table 11. Hours Register (RTCHOUR) Field Values (Continued)

### 7.6 Hours Alarm Register (RTCHOURA)

Figure 7. Hours Alarm Register (RTCHOURA)

| 7     | 6 |       | 0 |

|-------|---|-------|---|

| AMPM  |   | HAR   |   |

| R/W-0 |   | R/W–U |   |

**Legend:** R = Read; W = Write; -n = Value after reset, -U = Value unchanged by reset

| Field | Value |                                                                                                                                                            |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value | Description                                                                                                                                                |

| AMPM  |       | AM/PM select bit.                                                                                                                                          |

|       | 0     | Alarm time is set for AM or is in 24-hour mode.                                                                                                            |